New nanowire fabrication technique developed for next-gen spintronics

Spintronics is a new system that uses the spin of an electron, in addition to the charge state, to encode data, thereby making the entire system faster and more efficient. Ferromagnetic nanowires with high coercivity (resistance to changes in magnetisation) are required to realise the potential of spintronics, especially L10-ordered (a type of crystal structure) cobalt–platinum (CoPt) nanowires. Conventional fabrication processes for L10-ordered nanowires involve heat treatment to improve the physical and chemical properties of the material, a process called annealing on the crystal substrate; the transfer of a pattern onto the substrate through lithography; and finally the chemical removal of layers through a process called etching. Eliminating the etching process by directly fabricating nanowires onto the silicon substrate would lead to a marked improvement in the fabrication of spintronics devices. However, when directly fabricated nanowires are subjected to annealing, they tend to transform into droplets as a result of the internal stresses in the wire.

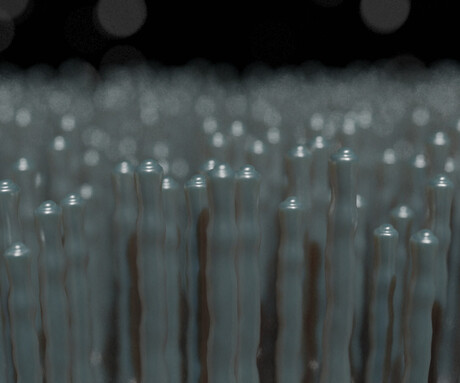

A team of researchers led by Professor Yutaka Majima from the Tokyo Institute of Technology have found a solution; the team reported a new fabrication process to make L10-ordered CoPt nanowires on silicon/silicon dioxide (Si/SiO2) substrates. The research findings were published in Nanoscale Advances. According to Majima, the researchers’ nanoscale-induced ordering method allowed the direct fabrication of ultrafine L10-ordered CoPt nanowires with the narrow widths of 30 nm scale required for spintronics. “This fabrication method could further be applied to other L10-ordered ferromagnetic materials such as iron–platinum and iron–palladium compounds,” Majima said.

The researchers first coated a Si/SiO2 substrate with a material called a ‘resist’ and subjected it to electron beam lithography and evaporation to create a stencil for the nanowires. Then they deposited a multilayer of CoPt on the substrate. The deposited samples were then ‘lifted-off’, leaving behind CoPt nanowires that were then subjected to high temperature annealing. The researchers also examined the fabricated nanowires using several characterisation techniques. The researchers found that the nanowires took on L10-ordering during the annealing process. This transformation was induced by atomic interdiffusion, surface diffusion, and large internal stress at the ultra-small 10 nm scale curvature radii of the nanowires. They also found that the nanowires exhibited a large coercivity of 10 kiloOersteds (kOe).

“The internal stresses on the nanostructure here induce the L10-ordering. This is a different mechanism than in previous studies. We are hopeful that this discovery will open up a new field of research called ‘nanostructure-induced materials science and engineering,’” Majima said.

The wide applicability and convenience of the novel fabrication technique is expected to contribute to the field of spintronics research.

A lighter, smarter magnetoreceptive electronic skin

Researchers have developed an innovative e-skin that facilitates a new level of interaction...

Single transistor used to implement neuromorphic behaviour

Researchers have demonstrated that a single transistor can mimic neural and synaptic behaviours,...

Novel fabrication technique for flexible electronics

Researchers have harnessed nature's intrinsic hierarchical fractal structures to improve the...