Better than ever — the second life of SMARC

By Peter Eckelmann, Product Marketing Manager, Embedded Boards, MSC Technologies

Thursday, 15 December, 2016

Recently the Standardization Group for Embedded Technologies (SGeT) announced revision 2.0 of the SMARC embedded module standard, and a number of companies showed early samples of related products at Embedded World 2016 in Nuremberg, Germany.

The resulting hype around this module specification is reason enough to take a closer look at this ‘ultimate’ standard for low-power processor modules and to highlight the differences between it and SMARC 1.1, Qseven and co.

The embedded module standards Qseven and SMARC are both under full control of the SGeT industrial group; therefore, many companies have sent delegates to the workgroups of both standards. Several members of the Qseven workgroup SDT.02 recently concluded that the Qseven standard was limited in its ability for essential extensions because of the 230-pin MXM-2 connector used for signal transmission down to the carrier board, which was fully used and unable to implement any additional signals. However, for applications in ‘real’ embedded designs there was an urgent need for the addition of signals usable for embedded hardware, exceeding the capacity of the Qseven connector.

As an alternative, the next-wider connector MXM-3 with 314 pins was discussed, which had already been in use for the SMARC 1.1 standard. At the same time, the SGeT workgroup SDT.01 had been called together again chartered with nothing less than the discussion and definition of the next-generation SMARC standard. Many company delegates from the Qseven workgroup came to the conclusion that the market was too small for two competing standards using the same connector but with different pin-out, and therefore joined the SMARC workgroup SDT.01 in order to help with the definition of the ultimate standard for low-power processor modules.

All important signals for embedded processor applications should remain available, but many older signals were removed in order to free up pins for new interfaces which provide faster speed and lower pin count resulting in an economic gain of functionality and performance. Therefore, the downward-compatibility from SMARC 2.0 to SMARC 1.1 was not an outspoken target and consequentially has not been achieved (or only with very many limitations). However, what has been achieved is the absolute fitness of the standard for both ARM/RISC and for x86 processors.

The SMARC standard features two different module sizes (82 x 50 mm and 82 x 80 mm) and therefore provides the makers of processor modules with sufficient flexibility to arrange new module products with the right mix of features and to find their optimum solution to the cost/performance trade-off. The small format provides enough space for single-chip SoCs (systems-on-chip) such as the Intel Atom or the i.MX6 from NXP (Freescale), to which some DRAM chips and maybe a Flash device will be added. If the module is targeted at higher functionality next to Ethernet, then further controller chips have to be added which may require the space offered by the larger module format. This will certainly be the case when RF functions such as WLAN, Bluetooth or 3G/4G data communication are required, so that a radio module will be added for which the module standard even specifies the placement of the antenna connectors.

Compared to the earlier SMARC 1.1 specification, many new interfaces were added for revision 2.0. These include a second LVDS interface which can be used to drive high-resolution LCDs in a two-channel arrangement together with the first LVDS channel (which will allow TFT resolutions up to Full-HD), or alternatively to operate two fully independent displays on single LVDS channels. The new standard also includes an alternative use of the LVDS pins for DSI or embedded DisplayPort (eDP). In order to achieve this, the parallel RGB lines for smaller LCD had to be dropped, but these are no longer required for recent displays and modern applications.

Next to the existing HDMI graphics port, the new standard encompasses a combined HDMI/DP port which is designated DP++ because it jointly implements the signals for DisplayPort, HDMI and DVI. Used together with the HDMI and LVDS ports, it opens up the possibility to drive up to three independent display systems (on the premise that the CPU platform of the module in questions does support triple independent displays at all).

SMARC 1.1 only provided one Gigabit Ethernet port, which now has been increased to two because modern applications are likely to demand two LAN ports in order to drive two Ethernet subnets and to keep apart communication realms (eg, the sensor and management domains in IoT gateways). Real-time trigger signals have been added to both Ethernet ports to give them RT capability according to IEEE1588.

SMARC Rev. 2.0 now provides up to four PCI Express interfaces, one more than 1.1 which for suitable platforms will allow an optional PCIe x4 operation resulting in a substantial performance gain. For USB the situation is similar, where the addition of three USB 2.0 ports results in the availability of up to six USB 2.0 next to up to two USB 3.0 ports. This underlines the fitness of the SMARC standard for x86 platforms which the creators of SMARC 2.0 had in mind, because these CPUs are always hungry for USB ports. For ARM/RISC platforms there are two USB ports which optionally also support Client functionality, and again for x86, one of the two SPI buses was enriched with optional eSPI functionality. Two audio interfaces can be used in parallel: one for I2S audio, as used by ARM processors, and one for HD audio, which is the standard codec for x86 CPUs.

Support for the less popular 8-bit MMC/SD card interface has been dropped, while 4-bit SDIO continues to be available for popular SD cards. Also, the parallel camera interface had to give way for the implementation of the new interfaces described above. But the standard continues to provide two MIPI CSI-2 interfaces: one with two lanes and a second with four lanes. This makes SMARC 2.0 the standard with the widest and most flexible camera interface of all established COM (computer-on-module) standards. But that is not all: SMARC 2.0 also provides a SATA port, 12 GPIOs, two CAN buses and four UART serial interfaces, which are always very important for embedded applications.

One of the most futureproof characteristics of the SMARC 2.0 standard is the large number of ‘reserved’ lines which are available on the MXM-3 connector, which are intended for future use when new and additional interfaces are to be included (and probably unknown to us today). With this capability for future extensions, the SMARC 2.0 standard ensures that it can be improved later on without obsoleting today’s carrier boards and/or modules. No hardware designed to the current SMARC 2.0 standard will be wasted when new revisions of SMARC are published. On the contrary, the standard provides for built-in upgradeability, thus protecting any investment into the current revision of the standard. Adding to the security of the right choice is the fact that all important module makers of embedded hardware were present in the SMARC workgroup of SGeT where the standard was defined, and have announced their own plans to offer products according to this standard.

MSC Technologies announced a first SMARC 2.0 module based on the ARM Cortex-A9 processors i.MX6 from NXP and has presented a suitable carrier board in the Mini-ITX format. The module MSC SM2S-IMX6 supports quad-, dual- and single-core CPUs as well as the recently introduced ‘Plus’ processors with their improved data throughput and higher graphics performance. The module comes in the smaller format 82 x 50 mm and provides up to 4 GB DRAM and up to 64 GB eMMC Flash. An integrated Micro-SD card slot enables the addition of Flash cards of almost any capacity, and this card or the eMMC Flash may be used for booting and may contain the operating system. The HDMI and LVDS graphics interfaces may drive displays up to a resolution of Full-HD.

The module supports PCI Express Gen. 2.0 and SATA II up to 3 Gbps as well as 5x USB 2.0 Host and USB 2.0 OTG (Host/Client) next to Gigabit Ethernet, 4x UART, 2x SPI, 2x I²C and 2x CAN. The MIPI CSI-2 interface can be used as camera input. The module will be available in variants for the full industrial temperature range -40 to 85°C as well as for commercial temperatures.

The internal design of the SMARC 2.0 module uses the same hardware core as the Qseven and nanoRISC modules from MSC, which are based on the i.MX6 processors from NXP. Therefore the complete software support is available from the start, from bootloader to operating system to the drivers and tools. This includes Yocto Linux and Android, while Windows Embedded Compact WEC2013 and WEC7) and further Linux variants will be added later on.

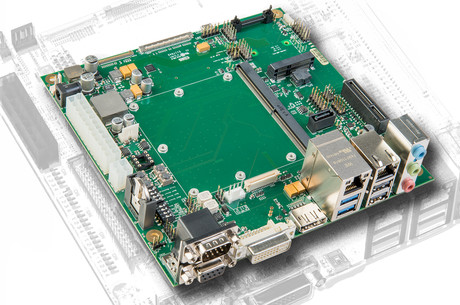

The carrier board MSC SM2-MB-EP1 comes in the Mini-ITX format 170 x 170 mm and gives access to most features of the SMARC 2.0 standard. With its diversity of interfaces, it is suitable for the evaluation of SMARC 2.0 modules but may be used — perhaps in a less-populated version — for not-too demanding volume applications.

Samples of the MSC SM2S-IMX6 module will become available as soon as SGeT has published the full extent of the SMARC 2.0 standard.

“We consider SMARC 2.0 the best and most futureproof standard for embedded modules in small form factors, and appreciate the support of all leading computer-on-module makers for this new standard,” said Jens Plachetka, manager embedded boards at MSC. “We have already begun the design of our second SMARC 2.0 module, which will be based on the next generation of Atom processors from Intel.”

Unlocking next-gen chip efficiency

By studying how heat moves through ultra-thin metal layers, researchers have provided a...

Ancient, 3D paper art helps shape modern wireless tech

Researchers have used ancient 3D paper art, known as kirigami, to create tuneable radio antennas...

Hidden semiconductor activity spotted by researchers

Researchers have discovered that the material that a semiconductor chip device is built on,...